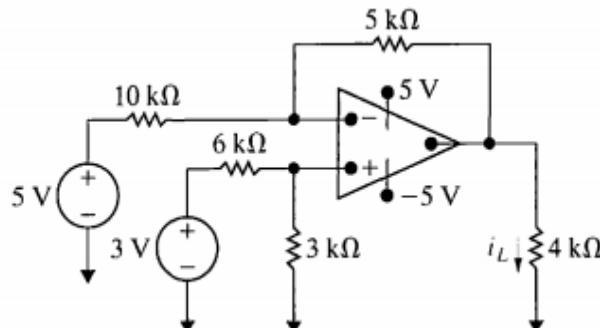

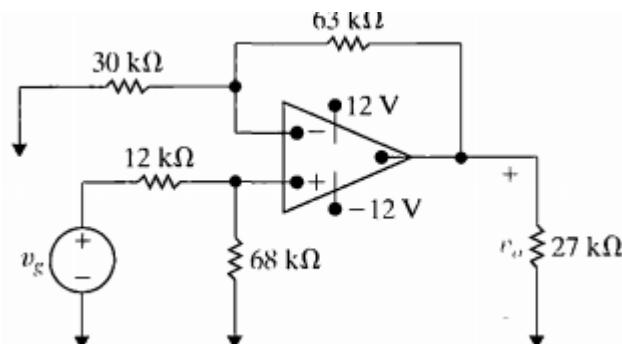

Q1: Find  $i_L$  (in micro amperes) in the circuit in Fig.1

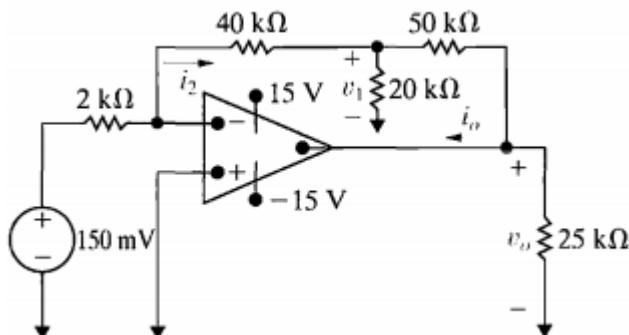

Q2: The op-amp in the circuit in Fig.2 is ideal. Calculate the following:  $v_1$ ,  $v_o$ ,  $i_2$  and  $i_o$

Fig.1

Fig.2

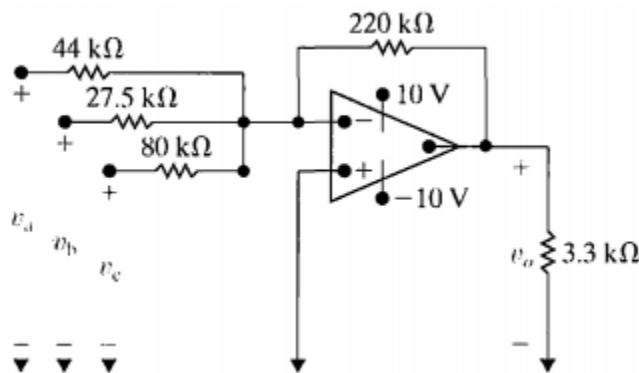

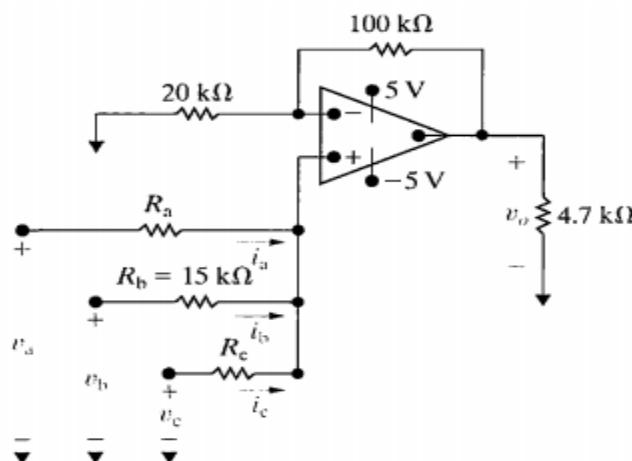

Q3: The op-amp in Fig.3 is ideal.

A) What circuit configuration is shown in this figure?

B) Find  $v_o$  if  $v_a=1\text{ V}$ ,  $v_b=1.5\text{ V}$  and  $v_c=-4\text{ V}$ .

c) The voltages  $v_a$  and  $v_c$  remain at  $1\text{ V}$  and  $-4\text{ V}$ ,

Respectively. What are the limits on  $v_b$  if the op-amp operates within its linear region?

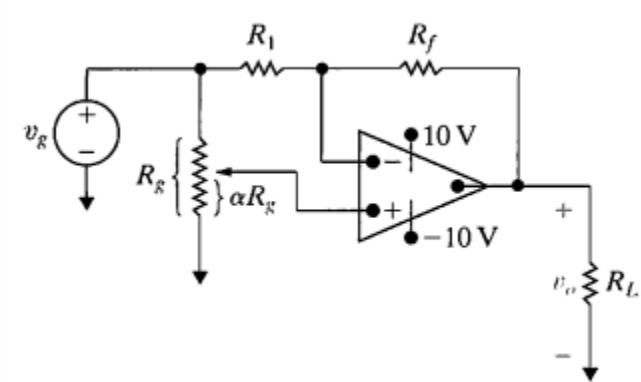

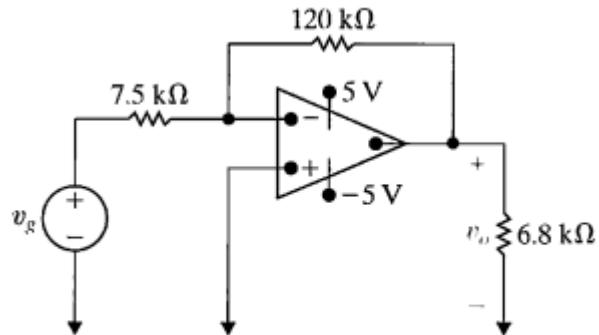

Q4: The op-amp in Fig.4 is ideal.

A) Calculate  $v_o$  when  $v_g$  equals  $4\text{ V}$ .

b) Specify the range of values of  $v_g$  so that the op-amp operate in linear region.

c) Assume that  $v_g$  equals  $2\text{ V}$  and that the  $63\text{k}$  Resistor replaced with variable what is its value to saturate the op-amp?

Fig.3

Fig.4

Q5: The circuit in Fig.5 is an non inverting summing amplifier. Assume the op-amp is ideal. Design the Circuit so that  $V_o = V_a + 2V_b + 3V_c$  a) Specify the numerical values of  $R_a$  and  $R_c$ . b) Calculate  $i_a$ ,  $i_b$ , and  $i_c$  (in micro amperes) when  $v_a=0.7\text{ V}$ ,  $v_b=0.4\text{ V}$ , and  $v_c=1.1\text{ V}$ .

Fig.5

Fig.6

**Q6:** The op-amp in the circuit of Fig.6 is ideal.

- Plot  $v_o$  versus  $\alpha$  when  $R_f=4R_1$  and  $v_g= 2V$ . Use increments of 0.1 and note by hypothesis that  $0<\alpha<1.0$ .

- Write an equation for the straight line you plotted in(a). How are the slope and intercept of the line related to  $v_g$  and the ratio  $R_f/R_1$ ?

- Using the results from(b), choose values for  $v_g$  and the ratio  $R_f/R_1$  such that  $v_o=-6 \alpha+4$ .

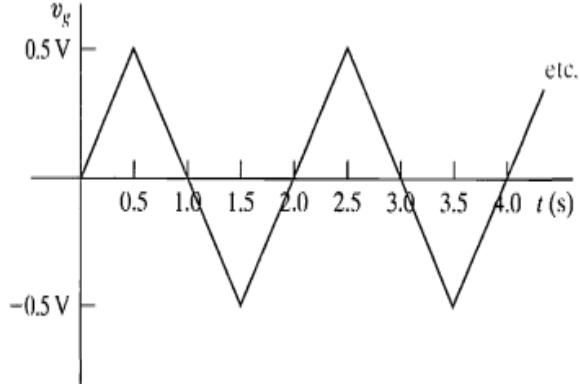

**Q7 :** The voltage  $v_g$  shown in Fig.7 (a) is applied to the Inverting amplifier shown in Fig.7 (b).

Sketch  $v_o$  versus  $t$ , assuming the op-amp is ideal.

(a)

(b)

Fig.7

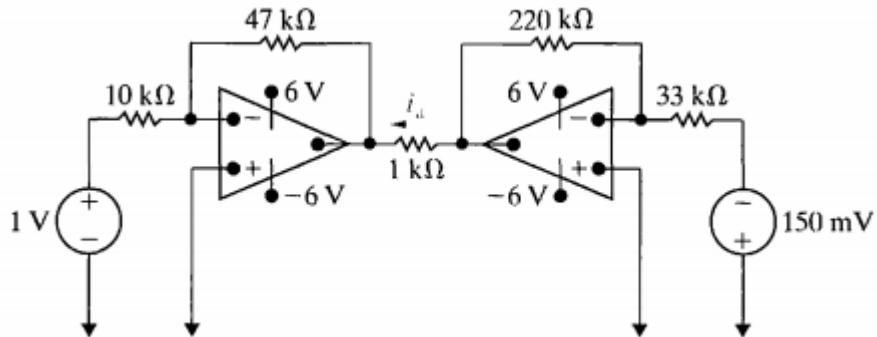

**Q8:** The op-amps in the circuit in Fig.8 are ideal .

- Find  $i_a$ .

- Find the value of the left source voltage for which  $i_a=0$ .

Fig.8

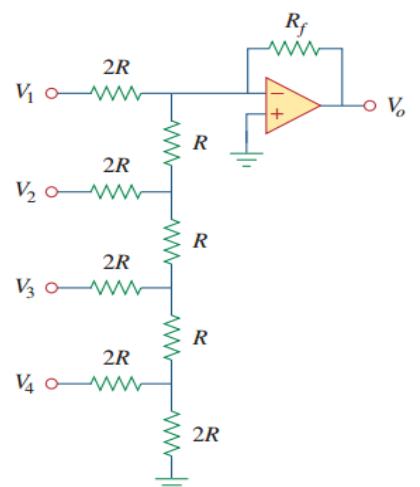

**Q9:** A four-bit R-2R ladder DAC is presented in Fig. 9

- Show that the output voltage is given by

$$-V_o = R_f \left( \frac{V_1}{2R} + \frac{V_2}{4R} + \frac{V_3}{8R} + \frac{V_4}{16R} \right)$$

- If  $R_f=12 \text{ k}\Omega$  and  $R=10 \text{ k}\Omega$ , find  $|V_o|$  for  $[V_1V_2V_3V_4] = [1011]$  and  $[V_1V_2V_3V_4] = [0101]$ .